GSJ: Volume 8, Issue 9, September 2020, Online: ISSN 2320-9186 www.globalscientificjournal.com

### MESSAGE PASSING INTERFACE OF COMPUTERS.

(A Case study of supercomputers using Ubuntu)

### Adamu A.I Ph.D

Computer Science Dept, Ibrahim Badamasi Babangida University Lapai-Nigeria.

#### Abstract

Message passing in the years might be an inborn segment in aspect of parallel computers but with PC configurations, each and every piece machine groups, running beginning with hand created to the absolute speediest rate of supercomputers on the planet, depending very well on the activities of the many individuals' center points that they encompass. On workstations that are based for item servers, with approximated excess of one thousand centers require been spreading. Concerning representation those number of centers over a bundle expands, those quick improvement in the complexity of the correspondence subsystem making message passing deferments over the interconnected certified execution issue in the execution of parallel programs. Specific instruments may be utilized to picture and observe that execution from asserting message passing for PC gatherings. Before a far reaching workstation cluster is applied, a follow based test framework uses little sum about the center points will help foresee those execution for message passim investigating greater setups.

**Keywords:** MPI, Parallel Computers, Ubuntu, Engineering Applications, Teaching and Processors

#### 1. Introduction

Truly, the two average ways to deal with correspondence between bunch hubs have been PVM, the Parallel Virtual Machine and MPI, the Message Passing Interface. However, MPI has now risen as the accepted standard for message

passing on PC clusters.PVM originates before MPI and was created at the Oak Edge National Research center around 1989 [4] [10]. It gives an arrangement of programming libraries that enable a processing hub to go about as a "parallel virtual machine". It gives run-time condition to message-passing, undertaking and asset the board, and blame notice and should be specifically introduced on each group hub. PVM can be utilized by client programs written in C, C++, or Fortran, and so on. Not at all like PVM, which has a solid execution, MPI is a detail instead of an explicit arrangement of libraries[1]. The determination rose in the mid 1990 out of dialogs between 40 associations, the underlying exertion having been upheld by ARPA and National Science Establishment. The structure of MPI drew on different highlights accessible in business frameworks of the time. The MPI determinations at that point offered ascend to explicit usage. MPI usage regularly utilize TCP/IP and attachment associations [10].

MPI is currently a broadly accessible correspondences demonstrate that empowers parallel projects to be written in dialects, for example, C, Fortran, Python, and so on The MPI detail has been executed in frameworks, for example, MPICH and Open MPI [6].

This benchmark is overwhelming once communication, particularly aggregate correspondence[2] [10]. It employments An. Amount for lessen Also show operations. This implies that it will presumably hint at An helter skelter. Execution punishment to utilizing those slower MPI operations As opposed to those local SCMP ones [4].

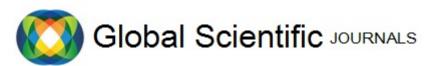

Figure 1: Steps involved in learning and teaching MPI configurations [3]

Those Most exceedingly bad the event situation will be with an expansive number from claiming processors and a little sum of information. For every processor — the obsessive the event might include an expansive processor show with particular case component. Of the grid An for every processor [4]. That declines the calculation will correspondence proportion [8]. Might harm those first system, in any case might make Indeed going more execution corruption should An. Framework in MPI with that's only the tip of the iceberg correspondence overhead. Those

MPI interchanges library will be an intricate bit from claiming programming. The MPI standard, which implements the usage in this proposal employments as a guide, comprises of nearly 120 capacities. This Section will be not an exhaustive reference but an implementor alternately client from claiming MPI might require something tangible and acceptable point by point. However it should provide those necessary platforms for learning of the essential structure of MPI and the mossycup oak regularly utilized capacities in the standard. [1] [2] [3].

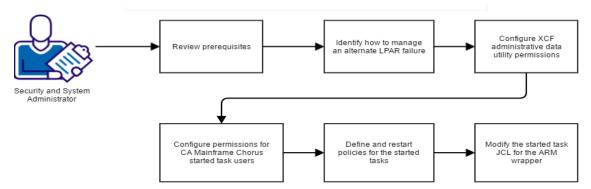

Figure 2(a): The flowchart of energy and security through the system[1]. There are Additionally a amount about language-specific libraries including Co-Array Fortran, secondary execution Fortran, What's more bound together parallel C; however, they bring not been depicted here to those purpose for curtness [8].

#### 2. Literature

Established parallel PC frameworks depends on various business (Bunks) the chips can't fulfill the superior necessities of various applications; not exclusively are these prerequisites expanding at a rate quicker than Moore's Law however the expense of these frameworks is restrictively high. To connect the execution hole however at a surprising expense, Application-Explicit Incorporated Circuit (ASIC) usage are regularly utilized. In any case, ASIC plans are not adaptable, but require restrictively high improvement expenses and set aside long opportunity to advertise [4].

FPGAs were once utilized in ASIC prototyping and stick rationale acknowledgment for advanced plans. Notwithstanding the most well known in FPGA creation, for all intents and purposes each chipmaker is seeking after reconfigurable registering these days, for example, Hewlett-Packard, Intel, NEC, Texas Instruments, Philips Gadgets and a few new businesses. We utilize the general term configurable in our examination to mean frameworks that are arranged at static time or potentially reconfigured at run time. Cray and SGI supercomputers immersing FPGAs have as of late turned out to be accessible also [8]. Every undercarriage in the Cray XD1 supercomputer contains six sheets, each containing a few processors and a FPGA [10].

A couple publications identified with incomplete fittings backing for MPI Previously, bunch situations have seemed as of late. In this way these results don't apply effectively with FPGA-

#### 3. Methodology

In parallelization unlike serial we utilize various systems for managing the dissemination of preparing over different hubs and the subsequent correspondence overhead. Some PC bunches, for example [7], utilization of distinctive processors for message going than those utilized for performing calculations. There is utilization of more than two thousand processors to improve the activity of its exclusive message passing framework, while calculations are performed by Xeon and Nvidia Tesla processors. One way to deal with lessening correspondence overhead is the utilization of nearby neighborhoods (likewise called areas) for explicit undertakings [2].

Here computational errands are allocated to explicit "neighborhoods" in the bunch, to build effectiveness by utilizing processors which are nearer to one another[8]. In any case, given that by and large the genuine topology of the PC group hubs and their interconnections may not be known to application engineers, endeavoring to adjust execution at the application program level is very troublesome [9].

Given that MPI has now risen as the accepted standard on PC groups, the expansion in the quantity of bunch hubs has brought about improvements with research to enhance the

based outlines[7]. Regardless of this fact, a Audit about these undertakings takes after Also suitableness execution correlations for our plan are exhibited in the test examination area about this paper. A FPGA-based execution about sun MPI2 apis for the sun Clint organize is news person Eventually Tom's perusing Fugier et al. [5]. Clint might have been formed In view of the perception that organize movement may be frequently all the bimodal holding vast Furthermore little packets requiring secondary throughput Furthermore low respectively; it utilizes two physically separate channels for these two unique sorts from claiming packets [3]. Should enhance the performance, new determinations for the usage of MPI works were furnished. Gigabit ethernet constitutes minimal effort result done highsounding interconnects. On the other hand, propelled solutions, for example, such that versatile sound interface (SCI), Myrinet, Quadrics and the Gigabyte framework Network, the execution by coordination move correspondence processors in the interface cards[6].

proficiency and versatility of MPI libraries. These endeavors have included research to diminish the memory impression of MPI libraries. From the soonest days MPI gave offices to execution profiling by means of the PMPI "profiling system". The utilization takes into consideration the perception of the passage and leave focuses for messages. Be that as it may, given the abnormal state nature of this profile, this kind of data just gives a look at the genuine conduct of the correspondence framework [6] [7]. The requirement for more data brought about the advancement of the MPI-Scrutinize framework. Examine gives a more definite profile by empowering applications to access state-changes inside the MPI-library. This is accomplished by enlisting callbacks with Scrutinize, and after that conjuring them as occasions triggers as message happen. Examining these systems can work with a perception framework [11].

There is utilization of positions from different frameworks, or play out its own following. It works at the assignment level, string level, and in a half breed organize. Follows regularly incorporate so much data that they are frequently overpowering. Along these lines there is ability to enable clients to picture and break down them. The purpose MPI gives to user-defined datatypes

may be powerful, in any case it necessities will be investigated for respects of the competencies of the equipment. For general, it permits particular case methodology with discretionary ends about information from discretionary areas over memory with an additional methodology which camwood get the individuals bits from claiming information Also set them wherever it longings too. SCMP's system help absolutely considers making a message starting with information appropriated all around memory [10]. However, it might require should be sent on a touching support on the remote side since best those remote side knows the thing that the design ought to be on that processor (the information design could make separate once both sides Concerning illustration in length Concerning illustration those number Also sorts from claiming information Questions may be those same). It is could be allowed that those sending processor Might gain the recipient's information design Toward conveying for it, yet the extra

arrangement might likely counterbalance any additions for this approach. Since the beneficiary processor will unpack the information during the destination, it might have been confirmed that unequivocally pressing whatever nonstandard information when sending might have been advantageous [9].

### 4. Performance analysis

With the expanding uniprocessor and SMP calculation control accessible today, interprocessor correspondence has turned into an imperative factor that constrains the execution of bunch of workstations. Numerous components including correspondence equipment overhead, correspondence programming overhead, and the client condition overhead influence the execution of the correspondence subsystems in such frameworks. A huge bit of the product correspondence overhead has a place with various message duplicating [8].

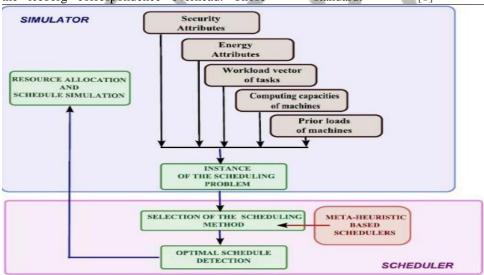

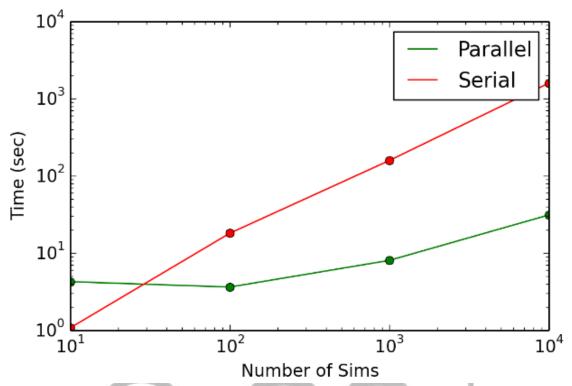

Figure 2(b): the benchmark shows an increase in parallel unlike the serial [2]

In any case, because of the way that messagepassing applications at the send side don't have the foggiest idea about the last get cradle addresses, unexpected arrival messages must be supported at a brief zone. In this paper, we have concocted distinctive message indicators at the recipient sides of interchanges. Generally, these message indicators can be effectively used to deplete the system and reserve the approaching messages regardless of whether the comparing get calls have not been posted yet. The execution of these indicators, regarding hit proportion, are very encouraging and recommend

expectation can possibly wipe out the vast majority of the rest of the message duplicates. We additionally demonstrate that the proposed indicators don't have affectability to the beginning message gathering call, and that they perform superior to (or possibly equivalent to) our recently proposed indicators[5] [9].

#### 5. Simulation

At the point when a huge scale, frequently supercomputer level, parallel framework is being produced, it is fundamental to have the capacity to explore different avenues regarding numerous arrangements and reenact execution. There are various ways to deal with displaying message passing proficiency in this situation, extending from explanatory models to follow based recreation and a few methodologies depend on the utilization of test conditions dependent on

"fake interchanges" to perform manufactured trial of message passing execution. Frameworks, for example, BIGSIM give these offices by permitting the reenactment of execution on different hub topologies, message passing and booking techniques [1].

Table 1: An example of matrix multiplication [6]

| 1000X1000 | 1500X1500 | 2000X2000 |

|-----------|-----------|-----------|

| 2.145     | 9.074     | 16.279    |

| 4.526     | 12.191    | 26.523    |

| 3.097     | 7.550     | 16.172    |

| 2.599     | 6.030     | 13.091    |

| 2.607     | 5.855     | 11.720    |

At the diagnostic dimension, it is important to display the correspondence time T in term of an arrangement of subcomponents, for example, the startup idleness, the asymptotic data transfer capacity and the quantity of processors. A notable model is Hockney's model which essentially depends on point to point correspondence, utilizing T = L + (M/R) where

M is the message estimate, L is the startup inactivity and R is the asymptotic data transfer capacity in MB/s. Xu and Hwang summed up Hockney's model to incorporate the quantity of processors, with the goal that both the idleness and the asymptotic data transfer capacity are elements of the quantity of processors [1] [11].

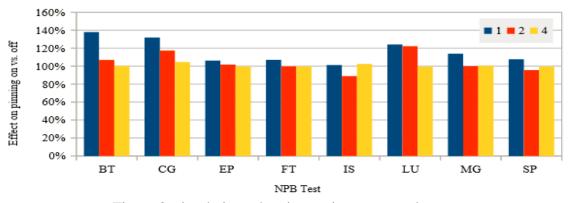

### Effect of pinning MPI ranks to cores

#### Variable I MPI PIN set ot on vs. off.

Figure 3: simulations showing various test results [6]

Figure 4: Comparisons between serial and parallel processes [6]

Explicit devices might be utilized to reenact and comprehend the execution of message passing on PC groups. For example, CLUSTERSIM utilizes a Java-based visual condition for discrete-occasion reenactment. In this methodology registered hubs and system topology is outwardly demonstrated.

Occupations and their term and intricacy are spoken to with explicit likelihood dispersions permitting different parallel employment booking calculations to be proposed and tried different things with. The correspondence overhead for MPI message passing would thus be able to be recreated and better comprehended with regards to vast scale parallel occupation execution. Other reenactment apparatuses incorporate MPI-sim and BIGSIM. MPI-Sim is an execution-driven test system that requires C

or C++ projects to work[11]. ClusterSim, then again utilizes a half breed more elevated amount demonstrating framework free of programming dialect utilized for program execution. Not at all like MPI-Sim, BIGSIM is a follow driven framework that reproduces dependent on the logs of executions spared in records by a different emulator program. BIGSIM incorporates an emulator, and a test system. The emulator executes applications on few hubs and stores the outcomes, so the test system can utilize them and reproduce exercises on an a lot bigger number of hubs [9] [11].

Table 2: System specifications of software and hardware's used [3]

| Application | OpenFOAM 4.X                           |                          |  |

|-------------|----------------------------------------|--------------------------|--|

| Benchmark   | MotorBike, 2M elements, 100 iterations |                          |  |

| System      | Wistron MiHawk                         | Wistron x86 system       |  |

| CPU         | P9 LaGrange DD2.2 * 2                  | Intel Xeon Gold 6148 * 2 |  |

| DIMM        | 32GB 2666MHz * 16 (1DPC)               | 64 GB 2666MHz * 24       |  |

| OS          | RHEL 7.5 ppc64le                       | Ubuntu 16.04 x86_64      |  |

| Compiler    | GCC 7.3.1                              | GCC 5.4.0                |  |

| MPI library | OpenMPI 1.10.7-1                       | OpenMPI 1.10.2-8         |  |

| Runtime     | <b>28.71</b> seconds                   | 43.57 seconds            |  |

The emulator stores data of successive execution squares for various processors in log documents, with every recording the messages sent, their sources and goals, conditions, timings, and so forth.

Table 3: Average time taken on cluster and multiprocess [7]

| Cluster Multiprocess, Average Time |               | Cluster MPI, Average Time |               |

|------------------------------------|---------------|---------------------------|---------------|

| Processes                          | Time(Seconds) | Processes                 | Time(Seconds) |

| 1                                  | 78.61         | 1                         | 98.41         |

| 2                                  | 47.35         | 2                         | 49.56         |

| 3                                  | 32.01         | 3                         | 33.07         |

| 4                                  | 24.39         | 4                         | 24.85         |

The test system peruses the log records and recreates them, and may star extra messages which are then likewise put away as SEBs. The test system would thus be able to give a perspective of the execution of substantial applications, in light of the execution follows given by the emulator on an a lot more modest number of hubs, before the whole machine is accessible, or arranged.

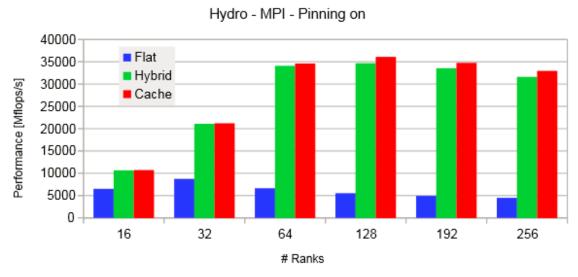

# Effect of High Bandwidth Memory settings

Figure 5: Differences in ranks and performance comparisons [11]

## 6. Summary

The principal venture to making this MPI execution might have been to peruse through the MPI standard Furthermore determine how those standard might be mapped of the abilities of the SCMP equipment. MPI purpose might have been that point executed, but if we recall previously, an incremental manner, for each work it might have been made. The code was created utilizing configuration standards with a concentrate on code reuse to determine its straightforwardness about change. That procedure permitted subsystems of the MPI usage will be totally rewritten now and again when it turned into reasonable they were insufflate the point when including new purpose. Following those library might have been complete, trying might have been performed for full MPI requisitions. This methodology is contrasted with the tests performed throughout advancement that tried distinctive capacities without respect to how they need aid utilized within a genuine provision. Throughout this time, bugs were discovered, edited and corrected, Also formerly neglected purpose might have been included of the library.

## 7. Conclusion

When the testing procedure was finished, some essential profiling was performed on the MPI applications. This helped center improvement of the most exceedingly awful parts of the MPI usage. Advancements were just performed in the event that they didn't significantly affect the comprehensibility or practicality of the code.

At long last, the capacity to translate MPI calls was important while investigating the MPI usage. The test system could demonstrate the status of the message lines related with every communicator amid the execution of the program, and that made it considerably more advantageous to recognize mistakes in message line the executives and to decide the status of a correspondence at a given piece of the program. This is a long ways from a test

system that gives enlist esteems and dismantled machine code.

#### References

- [1] Afsahi, A. (2015). "Design and Evaluation of Communication Latency Hiding/Reduction Techniques for Message-Passing Environments", *Ph.D. Dissertation, Department of Electrical and Computer Engineering, University of Victoria.*

- [2] Bailey, D. H., Harsis, T., Saphir, W., der Wijngaart, R. V., Woo, A. and Yarrow, M. (2017). "The NAS Parallel Benchmarks 2.0: Report NAS-95-020", Nasa Ames Research Center

- [3] Chu, H. (2016). "Zero-copy TCP in Solaris," *Proceedings of the USENIX Annual Technical Conference*, pp. 253–263.

- [4] Dubnicki, C., Bilas, A., Chen, Y., Damianakis S. and Li, K. (2017). "VMMC-2: Efficient Support for Reliable, Connection-Oriented Communication", *Proceedings of the Hot Interconnect*'97.

- [5] Dunning, D., Regnier, G., McAlpine, G., Cameron, D., Shubert, B., Berry, F., Merritt, A. M., Gronke, E. and Dodd, C. (2018). "The Virtual Interface Architecture", *IEEE Micro*, March–April, pp. 66–76

- [6] Lauria, M., Pakin, S. and Chien, A. A. (2014). "Efficient Layering for High Speed Communication: Fast Messages 2.x", Proceedings of the 7th High Performance Distributed Computing, HPDC7, Conference.

- [7] Lumetta, S. S., Mainwaring, A. M. and Culler, D. E. (2012). "Multi-Protocol Active Messages on a Cluster of

- SMPs", SC97: High Performance Networking and Computing Conference.

- [8] Mowry, T. and Gupta, A. (2013). "Tolerating Latency Through Software-Controlled Prefetching in Shared-Memory Multiprocessors", *Journal of Parallel and Distributed Computing*, 12(2), pp. 87–106

- [9] Takahashi, T., O'Carrol, F., Tezuka, H., Hori, A., Sumimoto, S., Harada, H., Ishikawa, Y. and Beckman, (2011)."Implementation Evaluation MPI on **SMP** of Cluster", *Proceedings of the PC-NOW9*: International Workshop on Personal Computer based Networks Of Workstations, inconjunction with PPS/SPDP'99.

- [10] Worley, P. H. and Foster, I. T. (2015). "Parallel Spectral Transform Shallow Water Model: A Runtime-tunable parallel benchmark code", *Proceedings of the Scalable High Performance Computing Conference*, pp. 207–214.

- [11] Zhang, Z. and Torrellas, J. (2016). "Speeding Up Irregular Applications in Shared-Memory Multiprocessors: Memory Binding and Group Prefetching", *Proceedings of the 22nd Annual International Symposium on Computer Architectures*, pp. 188–199.